台积电明年将量产5nm芯片「台积电早期5nm测试芯片良率80明年或迎来大规模量产」

本月,在 2019 IEEE IEDM 会议上,台积电用一篇新论文概述了其 5nm 工艺的初步成果。

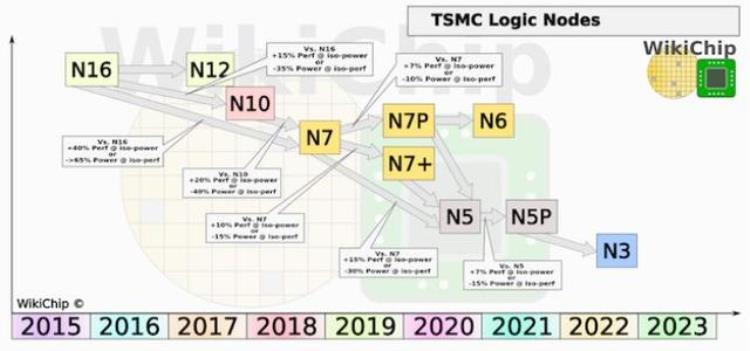

5nm 工艺,将会成为目前采用 N7 或 N7P 工艺的客户未来的新选择,因为它采用了这两个工艺的部分设计原则:新的 N5 工艺将保证 7nm 变体的全节点增加

10 层以上的 EUV 技术铺用,创新打破当今芯片掩模数量增加的膨胀传统,充分展现芯片设计 DTCO 效果,让测试芯片的逻辑密度增加 1.84 倍,能效增加 15%,功耗降低 30%,率先拉开 2020 HVM 的工艺预定序幕

本月,在 2019 IEEE IEDM 会议上,台积电用一篇新论文概述了其 5nm 工艺的初步成果。

5nm 工艺,将会成为目前采用 N7 或 N7P 工艺的客户未来的新选择,因为它采用了这两个工艺的部分设计原则:新的 N5 工艺将保证 7nm 变体的全节点增加,并在 10 层以上广泛使用 EUV 技术,减少了生产 7nm 过程中的步骤。新的 5nm 工艺还实现了台积电的下一代(第五代)鳍式场效应晶体管(FinFET)技术。

1 关键参数披露台积电声称,5nm EUV 工艺的整体改变在于:逻辑密度增加约 1.84 倍,能效增益 15%,功耗降低 30%。目前对 256Mb 的 SRAM 和一些逻辑芯片进行测试,平均产率为 80%,产率峰值大于 90%。因此,尽管可以将尺寸缩小到现代移动芯片,产率就低很多。该技术目前处于风险生产阶段,计划于 2020 年上半年实现量产。这意味着基于 5nm 共工艺的芯片将在 2020 年下半年准备就绪。

目前,台积电 7nm 工艺的晶体管密度约为 96.27MTr/mm2,这意味着新的 5nm 工艺应该在 177.14MTr/mm2 左右。

细节参数:

作为把控生产风险的一部分,工厂在生产大量的测试芯片,以验证工艺是否正常工作。对于 5nm,台积电披露了这样两款芯片:一款基于 SRAM,另一款结合了 SRAM、逻辑和 IO。

对于 SRAM 芯片,TSMC 展示了同时具有高电流(HC)和高密度(HD)的 SRAM 单元,其大小分别为 25000nm2 和 21000nm2。台积电正以目前最小尺寸的说法,积极推广其高密度 SRAM 单元。

关于组合芯片,台积电表示,该芯片由 30% 的 SRAM、60% 的逻辑(CPU/GPU)和 10% 的 IO 组成。芯片中有 256Mb 的 SRAM 单元,这意味着我们可以计算一下其面积大小。一个 256Mb SRAM 单元大小在 21000nm2,给出了 5.376mm2 的芯片面积。台积电表示,该芯片不包括自修复电路,这意味着我们不需要添加额外的晶体管来实现这一功能。如果 SRAM 单元占芯片的 30%,那么整个芯片应该在 17.92mm2 左右。

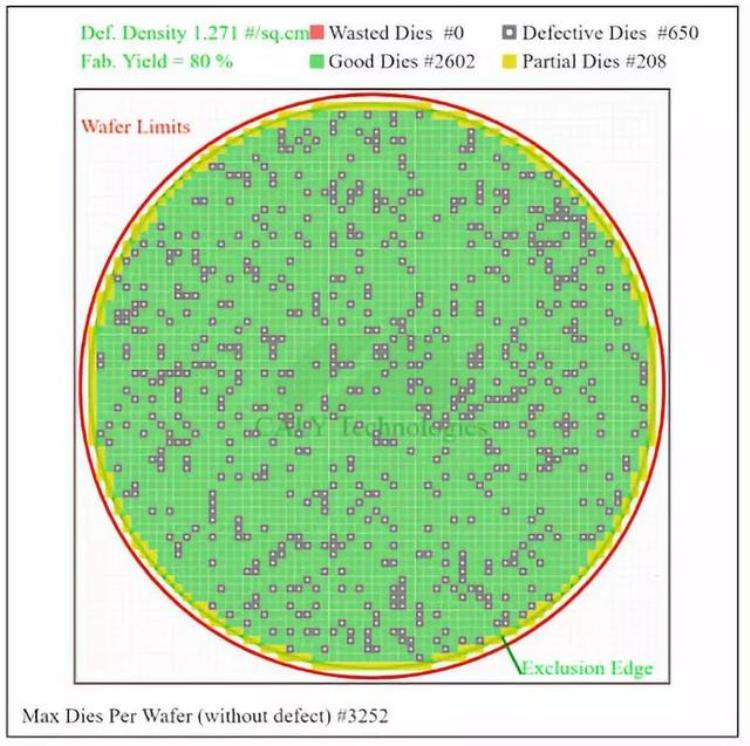

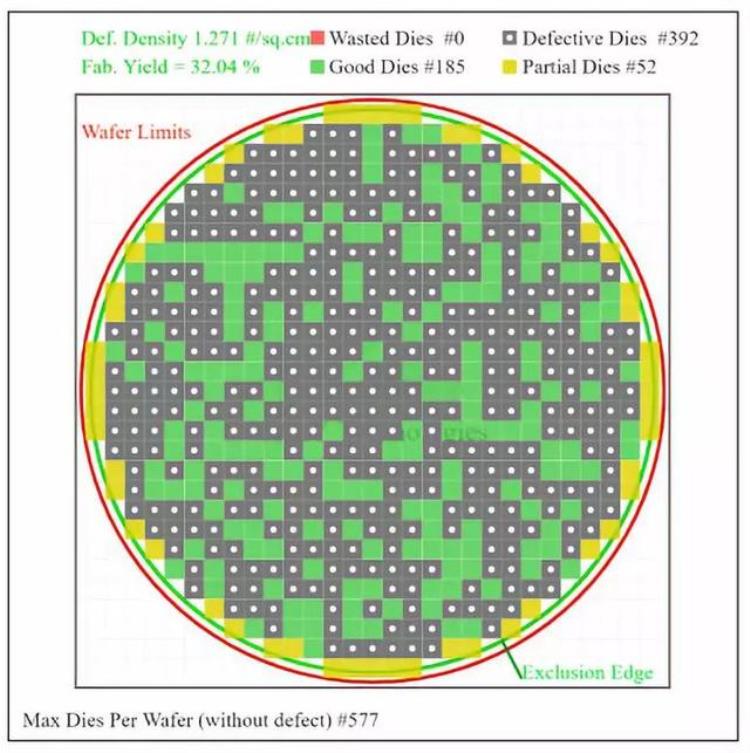

对于这种芯片,台积电公布的平均产率约为 80%,每片晶圆的产率峰值超过 90%。知道了成品率和晶粒尺寸,我们可以使用一个在线晶圆/晶粒计算器来推断缺陷率。简单起见,我们假设芯片是方形的,我们可以调整缺陷率,使成品率等于 80%。通过计算器,以 300mm 晶圆和 17.92mm2 的晶粒计算,每个晶圆中存在 3252 个晶粒。80% 的成品率意味着每个晶圆有 2602 个合格的晶粒,这相当于缺陷率为每平方厘米 1.271 个。

因此,一个 17.92mm2 的晶粒并不能表明这是一个高性能的现代工艺芯片。新工艺做文章的第一个芯片通常是移动处理器,特别是高性能移动处理器,因为它可以分摊新工艺的高成本。基于调制解调器的支持,芯片的尺寸在近年来被不断扩大,例如,在 7nm EUV 上构建的麒麟 990 5G 芯片,尺寸接近 110mm2。

有人可能会认为,AMD 的 Zen2 芯片组是更适用的芯片,因为它出自非 EUV 工艺,更容易转变为 5nm EUV。但这件事还需要一段时间,并需要通过使用高性能库将降低密集度。

这种情况下,让我们以台积电工艺第一代移动处理器,100mm2 芯片中的晶粒为例。同样,认为晶粒为正方形,缺陷率为每平方厘米 1.271 个,这时将保证 32.0% 的成品率。对于处于生产风险中的工艺来说表现是非常好了。100mm2 芯片可获得 32.0% 的收益率,对于一些想要领先的早期使用者来说,已经足够了。

(对于任何想要将这种缺陷密度与 10.35×7.37mm 的 Zen 2 芯片尺寸进行比较的人,这相当于 41.0% 的成品率。)

(注意:当我第一次读到它时,我只在 5.376mm2 SRAM 的情况下看到这个。通过计算,可以得到 4.26 的缺陷率,或者是 100mm2 的产率为 5.40%。这个数字很低。关于收益率具体指代的是哪种测试芯片,这篇报告有点模棱两可,因此我最初估计的收益率只有 5.4%。在与 Wikichip(国外知名半导体网站)的 David Schor 交谈后,他告诉我,即使是 32.0% 的收益率,对于 100mm2 芯片,的风险生产来说也有点低,除非你愿意冒很大风险去做。)

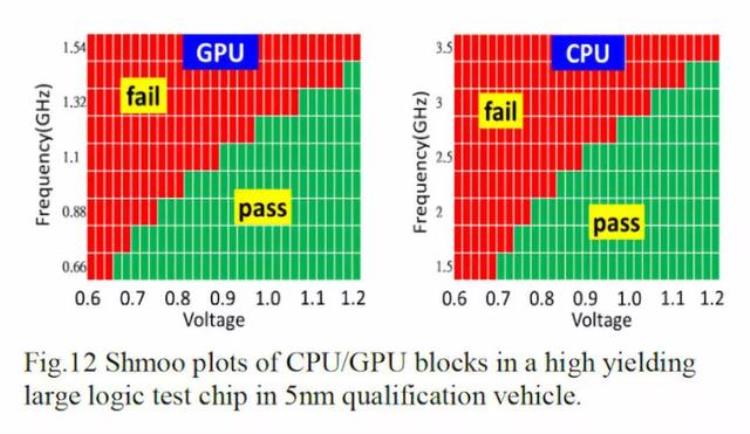

2 台积电芯片测试:CPU和GPU频率当然,芯片测试出的产率也许就意味着什么。一个成功的芯片可能随时处在就绪的状态,而缺陷率从来不被纳入对工艺能驱动多大功率和频率的思考范围内。作为本次公开的一部分,台积电还提供了一些测试芯片的「shmoo」电压与频率的关系图作为展示。

根据图片显示:

对于 CPU,在 0.7V 时频率为 1.5GHz,在 1.2V 时上升至 3.25GHz。

对于 GPU,在 0.65V 时频率为 0.66GHz,在 1.2V 时上升至 1.43GHz。

有人可能会说,这些数据并不是特别有用:CPU 和 GPU 的设计存在非常大的不同,一个深度集成的 GPU 可以根据它的设计,在相同电压下获得更低的频率。不幸的是,台积电没有透露他们用什么作为 CPU/GPU 的示例,尽管 CPU 部分通常被认为是 Arm 内核(尽管它可能只是这么大芯片上的一个内核)。这通常取决于流程节点的主要合作伙伴是谁。

3 IO演示:PAM4未来芯片的关键要素之一是支持多种通信技术的能力,台积电在测试芯片中还包括一个设计用于实现高速 PAM-4 的收发器。

我们已经在其他工艺上看到了 112Gb/s 的收发器,台积电能够在这里以 0.76pJ/bit 的能效实现 112Gb/s。为了进一步提高带宽,台积电将在眼图中的公差范围内,以 0.96pJ/bit 能效够获得 130Gb/s 的带宽。这对任何基于 PAM-4 的技术来说都是个好兆头,比如 PCIe 6.0。

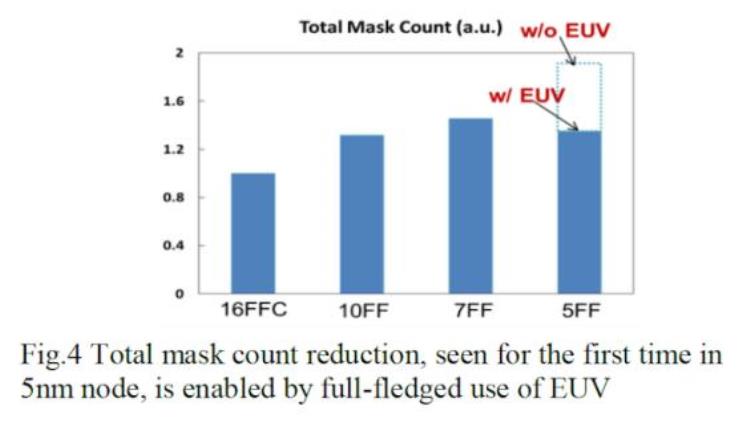

4 使用EUV:减少掩模数量在 193nm ArF 浸没光刻技术上投入大量心思的后果,就是掩模在越发复杂的处理器中的数量越来越多。

在过去,28nm 存在 30-40 个掩模,现在在 14nm 和 10nm 上有超过 70 个掩模;而根据报道,一些前沿工艺技术已经做到超过 100 个掩模。在本次报告中,台积电表示,将在 10 层以上广泛使用 EUV 的设计中,首次实际减少带有新工艺节点的掩模数量。

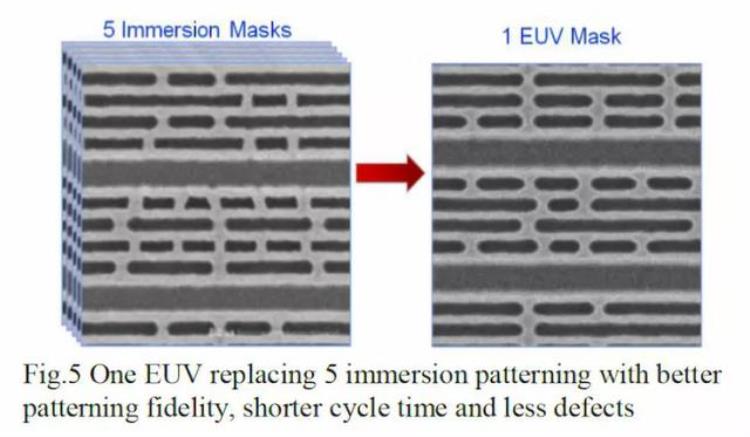

EUV 的好处在于,能够用一个 EUV 步骤替换四个或五个标准的非 EUV 掩蔽步骤。这可以归结为 EUV 技术在硅层提供的更高的定义。另一方面,单台 EUV 机器(每个掩模每小时 175 片晶圆)的吞吐量远低于非 EUV 机器(每个掩模每小时 300 片晶圆),但是 EUV 的速度应乘以 4-5 这个数字范围,来获得比较吞吐量。应该说,台积电的广泛使用将大大减少掩模数量。归根结底,这只是小幅下降。

假设 16FFC 工艺有 60 个掩模,10FF 工艺有 80-85 个掩模,7FF 更多,有 90-95 个掩模。有了 5FF 和 EUV,这个数字会回到 75-80;而没有 EUV 的话,这个数字可能超过 110。假设有足够的 EUV 机器可以运行,将简化事情的复杂程度。最近的报告指出,ASML 在 2019 年的订单发货方面落后,并计划在 2020 年再制造 25-27 台,而 2020 年至少需要 50 台机器。

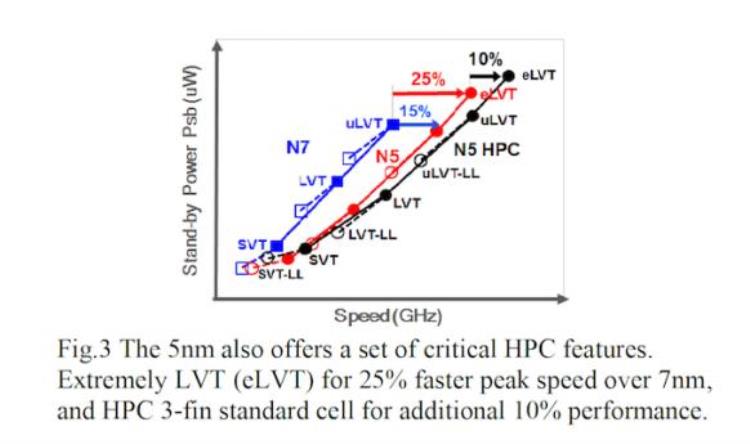

5 5nm晶体管类型IEDM 论文的一部分,描述了七种不同类型的晶体管可供客户使用。我们已经提到了新的类型,高端的 eVT 和低端的 SVT-LL,但是这里有一系列根据泄漏和性能要求使用的选项。

三种主要类型是 uLVT、LVT 和 SVT,这三种类型都有低渗漏(LL)变体。eLVT 在上部,从 uLVT 到 eLVT 有一段距离。

6 设计技术协同优化(DTCO)的效果今年 IEDM 有一个很明显的特点就是 DTCO 的使用。简言之,DTCO 本质上是一个工艺优化的分支,是芯片设计的结果,也就是说,设计一个整体芯片并将其放在硅上是非常容易的,但是为了获得最佳的性能/功率/面积,需要根据问题对硅的工艺节点进行优化。这种协同优化的效果非常显著:PPA 中另一个工艺节点的替代物还禁不起深究,这也意味着它需要时间来完善。

DTCO 的一个缺点是,当应用于给定的流程或设计时,它意味着未来任何第一代工艺节点在技术上都比上一代整体的最佳版本差,或者充其量打成平手,但成本要贵得多。因此,为了改进先前的处理技术,要在新节点至少一代上应用 DTCO,才能使其变得可行,从而使推出的时间变得更长。

对于我们现在生活的这个世界来说,这是一件永恒的艺术品。英特尔、台积电(TSMC)和三星(Samsung)必须在特定产品的每个新工艺(以及每个工艺变体)中应用一些 DTCO。至少对台积电而言,某些公司可能会从一些 DTCO 改进中获益,以帮助这些公司获得额外的绩效收益。但事实上,仅仅是用 DTCO 保持平衡,意味着我们得到了工艺节点声明的进一步延伸:如果它没有 DTCO 的形式,那么它就不值得发布,因为没有人会想要它。

谢天谢地,台积电在 IEDM 的 5nm 论文中,直接谈到了 DTCO 这个话题。5nm 测试芯片采用了 DTCO 的元素,而不是粗暴地强制执行设计规则,这使得设计规则选择可伸缩地在总体上减少了芯片尺寸的 40%。因此,总的测试芯片尽管尺寸在 17.92mm2,实际更像 25.1mm2,产率为 73% 而不是 80%。这听起来不算多,但在这种情况下,每一点都有帮助:有了 DTCO 的这一元素,它使台积电能够引用密度增加 1.84 倍,速度提高 15%,功率降低 30%。

台积电没有披露的一个明显的数据点,是其翅片间距大小的确切细节,或是与聚沥青(cpp)的联系,后者在披露新工艺节点的风险生产时经常被引用。我们希望台积电在适当时候公布这些数据。

文章评论